8b/10b编码

概要[Abstract]

8b/10b编码是一种可以保证DC平衡的编码机制,即通过这种编码机制,8位的数据变成了10位,但是数据流中的“0”和“1”基本保持平衡。8b/10b编码是目前许多高速串行总线中的编码机制,如USB3.0、1934b、Serial ATA、PCI Express、Infini-band、Fibre Channel、RapidIO等总线或者网络。

本设计中,将8b/10b转换分为两步实现,第一步将低五位变成六位,第二步将高三位变为四位,即5b/6b转换和3b/4b转换。为表述方便,将八位数据HGFEDCBA记为D.x.y,其中x代表低五位EDCBA对应的十进制数,y代表高三位HGF对应的十进制数。在转换过程中,利用极性偏差(running disparity,RD)[注:RD只能为-1和+1]来控制数据流的DC平衡,给定初始的RD=-1(也可以为+1),在5b/6b转换之后根据6b数据的不均等性(disparity)[注:不均等性即“1”和“0”的个数差值]来决定输出的RD,输出的RD值进一步决定3b/4b的译码方式,而4b数据的不均等性又决定输出的RD值,然后输出的RD又作为下一个8b/10b转换的初始RD值,RD值和数据转换的关系如下图所示:

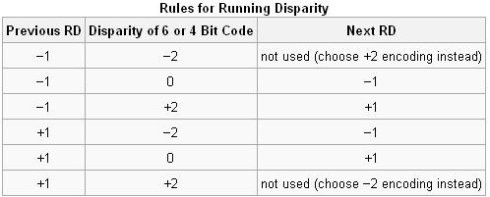

对于RD的值,按下表的规则来确定:

可以很简单的理解该表:当6b或者4b的数据中“0”和“1”个数相等时,RD保持不变,当“0”和“1”个数不相等时,RD变值。

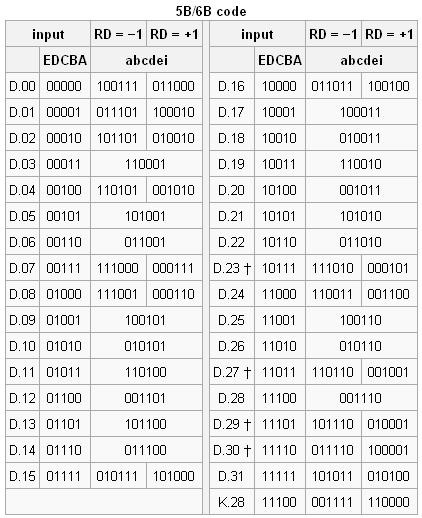

5b/6b的编码规则如下:

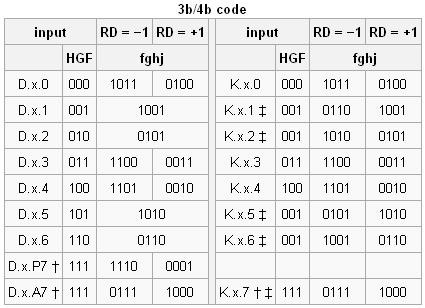

3b4b编码的规则如下:

其中8b数据HGFEDCBA的低五位经过5b/6b编码将EDCBA编码成abcdei,高三位HGF经过3b/4b编码成fghj,最终形成10b数据abcdeifghj.

数据编码时分为一般代码和控制代码,一般代码的前缀为“D”,控制代码的前缀为“K”,对于8b的低五位为28的数据,利用K.28.y进行编码,当x=23,27,29,30且y=7时,也利用K.x.7进行编码,其他均按一般代码的编码规则编码,即控制码组如下:

除此之外,在一般代码的编码规则中,只有D.x.7的编码情况比较特殊,分为D.x.A7和D.x.P7,D.x.A7用在当x=17,18,20且RD=-1或者当x=11,13,14且RD=+1时,其他的D.x.7全按照D.x.P7方式进行编码。

这些不一样的编码方式都是为了尽量保证编码中的“0”和“1”的平衡。

在我的设计中,利用两个不一样的时钟信号触发编码过程,两个时钟信号如下:

利用两个时钟编码原因是:在一个8b数据转换中,5b/6b转换和3b/4b转换及输出的RD(RD1)赋值给输入的RD(RD2)[注:这是为了给下一个8b/10b转换赋初始RD值]需要在不同的时刻完成(为了避免数据的竞争而出现错误)。

两个时钟clk和clk1均是周期为4ns的时钟信号,只不过clk1比clk延迟了1ns,在clk的上升沿时,完成5b/6b的转换,在clk1的上升沿时,完成3b/4b的转换,在clk的下降沿时,完成输出的RD1对输入的RD2的赋值以及输出10b数据。

在本设计中,一共分为五个小模块:atoal(取8b数据的低五位)、atoah(取8b数据的高三位)、fivesixtransform(5b/6b转换)、threefourtransform(3b/4b转换)以及blbhtob(输出10b

数据),在设计中,为了表示简单,将RD设置成一位的数据,其值有“0”和“1”,故用“0”表示RD=-1,用“1”表示RD=+1。

需要注意的是,每一个8b数据的输入要在clk为低电平时完成,否者就会造成数据丢失。

在验证过程中,输入值依次取a=11110001,11101011,00011100,11111101,00000000;

预期结果分析如下:

10001(RD=-1)——100011(RD=-1),111(RD=-1)——0111(RD=+1) 输出:1000110111

01011(RD=+1)——110100(RD=+1),111(RD=+1)——1000(RD=-1)输出:1101001000

11100(RD=-1)——001111(RD=+1),000(RD=+1)——0100(RD=-1)输出:0011110100

11101(RD=-1)——101110(RD=+1),111(RD=+1)——1000(RD=-1)输出:1011101000

00000(RD=-1)——100111(RD=+1),000(RD=+1)——0100(RD=-1)输出:1001110100

运行结果如下:

输出结果依次为:237(1000110111)、348(1101001000)、F4(0011110100)、2E8(1011101000)、274(1001110100)

运行结果与预期分析结果一致,且6b和4b数据以及RD也与分析结果一致。

下载[Download]:design/10110.rar

TEL:+86-18562888017

TEL:+86-18562888017

Email: robei[at]robei.com

Email: robei[at]robei.com